University of Alabama at Birmingham UAB Digital Commons

## All ETDs from UAB

**UAB Theses & Dissertations**

2014

# A Low-power Multichannel Telemetry System for High-speed Wireless Neural Recordings

Yangguo Li University of Alabama at Birmingham

Follow this and additional works at: https://digitalcommons.library.uab.edu/etd-collection

#### **Recommended Citation**

Li, Yangguo, "A Low-power Multichannel Telemetry System for High-speed Wireless Neural Recordings" (2014). *All ETDs from UAB*. 2274. https://digitalcommons.library.uab.edu/etd-collection/2274

This content has been accepted for inclusion by an authorized administrator of the UAB Digital Commons, and is provided as a free open access item. All inquiries regarding this item or the UAB Digital Commons should be directed to the UAB Libraries Office of Scholarly Communication.

## A LOW-POWER MULTICHANNEL TELEMETRY SYSTEM FOR HIGH-SPEED WIRELESS NEURAL RECORDINGS

by

YANG-GUO LI

## MOHAMMAD R. HAIDER, COMMITTEE CHAIR KARTHIKEYAN LINGASUBRAMANIAN ROTEM A. ELGAVISH NASIM UDDIN B. EARL WELLS

### A DISSERTATION

Submitted to the faculty of the University of Alabama at Birmingham, in partial fulfillment of the requirements of the degree of Doctor of Philosophy

### BIRMINGHAM, ALABAMA

# A LOW-POWER MULTICHANNEL TELEMETRY SYSTEM FOR HIGH-SPEED WIRELESS NEURAL RECORDINGS

#### YANG-GUO LI

#### COMPUTER ENGINEERING

#### ABSTRACT

The advances in microelectronics and wireless communication are going to change our lifestyles and benefit our healthcare system in the foreseeable future. New conception named "Ubiquitous Healthcare" has been proposed. It envisions a continuous, real-time, remote monitoring on the health conditions of people through the wireless communication network. Traditional biosignal monitoring devices need wire-connections for the recording, which may cause skin rupture and body infection. The physical connections also limited the number of the integrated recording channels. A low-power implantable multichannel telemetry system which can be implanted in the body and transmit recordings wirelessly can solve the problem of the traditional method. However, the design of such a low-power multichannel telemetry system is challenging. In this study, we have designed a telemetry system which possesses several merits in terms of power dissipation, system sensitivity, and data transmission rate. Research efforts have been made to address the critical design challenges of low-power consumption, high data rate communication, low cost and miniaturization, by employing subthreshold MOSFET based design, noise optimization, neuromorphic architecture and judicious use of positive and negative feedbacks. As a sensor signal acquisition unit, a low-power low-noise self-biased CMOS amplifier has been demonstrated. Modified spike detection algorithm, frequency-enhanced nonlinear energy operator (fNEO) and energy-of-derivative (ED), have been formulated and validated through CMOS all-inverter based circuit architecture. For spectrum efficient high data rate communication, a modified Hermite polynomial based ultra-wideband pulse generation schemes have been proposed and demonstrated with neuromorphic circuits.

Keywords: Analog Circuits, RF Circuits, Telemetry System, Wireless Communication.

## DEDICATION

TO MY BELOVED PARENTS, WIFE, AND SON.

## ACKNOWLEDGEMENTS

First and above all, I praise God, whose blessings make me who I am today. The almighty provide me the opportunity, spirit, and capability to proceed successfully.

This dissertation would never be finished without the guidance of my committee members, the help from my friends, and the support from my dear family. I would like to express my sincere gratitude to my advisor, Dr. Mohammad Haider. His guidance, patience, and encouragement enabled me to complete this dissertation. Dr. Mohammad Haider's knowledge, research experience and enthusiasm on work motivate me during my entire study and set a model for my future career.

I also express my sincere thank to Dr. Karthikeyan Lingasubramanian, Dr. Rotem Elgavish, Dr. Nasim Uddin, and Dr. Earl Wells for serving on my committee. Thank you all for spending your valuable time on my dissertation. Your comments and feedbacks are very important for this work. Special thanks to Dr. Earl Wells for driving all the way from Huntsville on my defense day.

I would like to thank my lab fellow and good friend, Qingyun Ma, for the happy-time and hard-time that we have experienced together in study and job seeking. It is lucky for me to have you and great pleasure to work with you. Also gives my gratitude to my friends in the graduate program, Fan Xiong, Vikas Singal, Manar Mohamed, Vinaya Shrestha, Shanshan Yang, and Pawan Karki, who always give me encouragement and support at the right moments. We had a great time working together. I value and appreciate our friendship. I would also show my gratitude to other group members A K M Arifuzzman, Laxmi Ray, and Kushal Pradhan. Special thanks go to my close friend Qizhuo Huang who encourages me all the time and provides lots of help in daily life. Also thank to Dr. Lei Liu from optometry, who always gives me valuable suggestions about study and living in US. I owe many thanks to the faculty and staff in the ECE department in UAB. I am deeply indebted to the department for the financial support all through my graduate study here at UAB. Thanks to the current chair Dr. Murat Tanik, previous chair Dr. Allen Tannenbaum, Dr. Yehia Massoud and Dr. Gregg Vaughn. I truly appreciate their great help. Many thanks go to Dr. Tom Jannett, Dr. Yi Gao, Dr. Dalton Nelson, Dr. Dale Callahan, and Jon Marstrander. Thanks for being great professors and friends to me. Special thanks to Janice Hofman, Sandra Muhammad, and Debbie Harris, who have offered me tremendous help with paperwork and lab equipment.

Last but not least, I would like to give my deepest thanks and appreciation to my family. To my father Tingsheng Li, my mother Wanxiu Yang, my wife Yue Song, and my lovely son James Li: thank you all for being so supportive to me. Without you I would not have the motivation and courage to complete this work. Thanks for always standing by me and giving me selfless love.

# Contents

| ABSTRACT                                                                                                                                                                                                                                                                                                                                     | ii                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| DEDICATION                                                                                                                                                                                                                                                                                                                                   | iii                                    |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                             | iv                                     |

| List of Tables                                                                                                                                                                                                                                                                                                                               | viii                                   |

| List of Figures                                                                                                                                                                                                                                                                                                                              | ix                                     |

| 1. INTRODUCTION       Background         Background       Background         Motivation       Background                                                                                                                                                                                                                                     | 1<br>1<br>2                            |

| <ol> <li>LITERATURE REVIEW</li> <li>Research Approaches</li> <li>2.1. Specific Aims</li> </ol>                                                                                                                                                                                                                                               | 5<br>7<br>7                            |

| <ul><li>Aim 1: Development of a low-power low-noise biopotential amplifier for signal amplification</li><li>Aim 2: Development of a low-power high-sensitivity spike detector for data</li></ul>                                                                                                                                             | 7                                      |

| Compression                                                                                                                                                                                                                                                                                                                                  | 8<br>8                                 |

| 3. BIOSIGNAL AMPLIFIERS         An Ultra-Low-Power Bioamplifier         Introduction of Ultra-Low-Power Bioamplifier         Proposed Ultra-low-power Bioamplifier         Noise analysis on the proposed bioamplifier         Simulation Results         Summary of Ultra-Low-Power Bioamplifier         A Low-Noise Gain-Tunable Amplifier | 10<br>10<br>12<br>13<br>16<br>19<br>20 |

| Introduction of Low-Noise Gain-Tunable Amplifier                                                                                                                                                                                                                                                                                             | 20<br>21<br>23<br>24<br>26             |

| Introduction of Amplifier With Optimized Noise Efficient FactorThe Proposed Low-noise Biopotential AmplifierNoise Performance OptimizationNEF theoretical limit of a folded cascode amplifier                                                                                                                                                | 28<br>29<br>31<br>32                   |

| Noise performance optimization under the NEF theoretical limit                                                                                                                                                                                                                                                                               | 33                                     |

| Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35<br>37                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| <ul> <li>4. NEURAL SPIKE DETECTOR.</li> <li>Low-Power High-Sensitivity Spike Detectors</li> <li>Introduction of Spike Detectors</li> <li>Background on Detection Algorithms</li> <li>Proposed Spike Detection Algorithms</li> <li>The Low-power Analog Implementations</li> <li>Simulation Results and Statistical Analysis</li> <li>Summary of Spike Detectors</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39<br>39<br>39<br>41<br>42<br>46<br>48<br>52                                                       |

| <ul> <li>5. POWER-EFFICIENT TRANSMITTERS</li> <li>Low-Power Neuromorphic Circuits</li> <li>Introduction of Neuromorphic Circuits</li> <li>Neuromorphic sensor circuit</li> <li>Simulation Results</li> <li>Summary of Neuromorphic Circuits</li> <li>An Inductorless Low-Power Tunable Sinusoidal Oscillator</li> <li>Introduction of Sinusoidal Oscillator</li> <li>Four-electrode Micro-impedance Spectroscopy</li> <li>Proposed Sinusoidal Oscillator</li> <li>Simulation Results</li> <li>Summary of Sinusoidal Oscillator</li> <li>An Efficient Orthogonal Pulse Set Generator</li> <li>Introduction of Pulse Set Generator</li> <li>Background on Modified Hermite Pulses</li> <li>Proposed Efficient MHP Set Generator</li> <li>Proposed Neuromorphic MHP Set Generator</li> <li>Summary of Pulse Set Generator</li> <li>Summary of Pulse Set Generator</li> </ul> | 54<br>54<br>55<br>60<br>62<br>63<br>64<br>65<br>66<br>69<br>70<br>72<br>73<br>74<br>76<br>77<br>82 |

| 6. CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84                                                                                                 |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 87                                                                                                 |

## **List of Tables**

| 1 | Comparison of the Proposed Bioamplifier with the Previously Reported Works            | 19 |

|---|---------------------------------------------------------------------------------------|----|

| 2 | Performance of the proposed amplifier and other state-of-art designs                  | 24 |

| 3 | Transistor Aspect Ratios Used In the Proposed Amplifier                               | 35 |

| 4 | A comparison of reported biopotential amplifiers.                                     | 38 |

| 5 | Sensitivity comparison of three spike detectors.                                      | 46 |

| 6 | The resistivities of various tissues presented in terms of the mean values and $95\%$ |    |

|   | confidence intervals                                                                  | 68 |

# List of Figures

| 1  | (a) A ubiquitous healthcare system. (b) An implantable multichannel telemetry       |    |

|----|-------------------------------------------------------------------------------------|----|

|    | system used for BMI robotic arm control. (Picture is from Nathan C. Rowland, etc.   |    |

|    | 2013 [ <b>1</b> ])                                                                  | 3  |

| 2  | The block diagram of a multichannel telemetry system. MUX: multiplexer              | 4  |

| 3  | Biopotential recording system.                                                      | 11 |

| 4  | Characteristics of typical biosignals.                                              | 12 |

| 5  | (a) Bioamplifier with a high-pass filter for DC suppression. (b) Schematic of the   |    |

|    | proposed bioamplifier.                                                              | 14 |

| 6  | Gain and bandwidth profile                                                          | 16 |

| 7  | Monte Carlo Simulation. (a) Monte Carlo Simulation results of input-referred        |    |

|    | noise. (b) Monte Carlo Simulation results of THD when input $V_{pp}$ =500 $\mu$ V   | 17 |

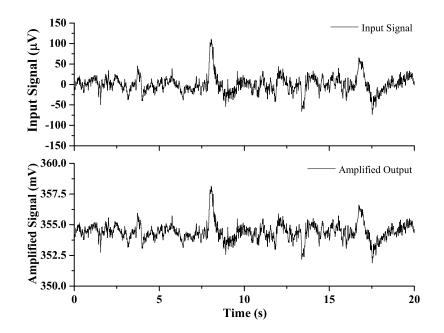

| 8  | Input EEG signal and amplified output                                               | 18 |

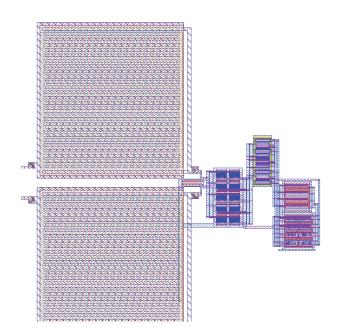

| 9  | The layout of the proposed bioamplifier                                             | 18 |

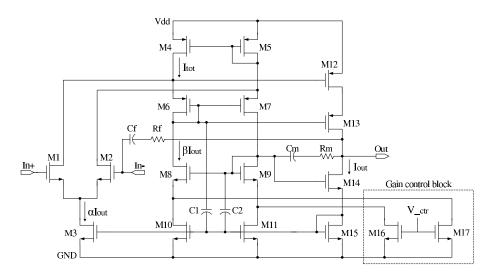

| 10 | Schematic of the proposed biopotential amplifier.                                   | 21 |

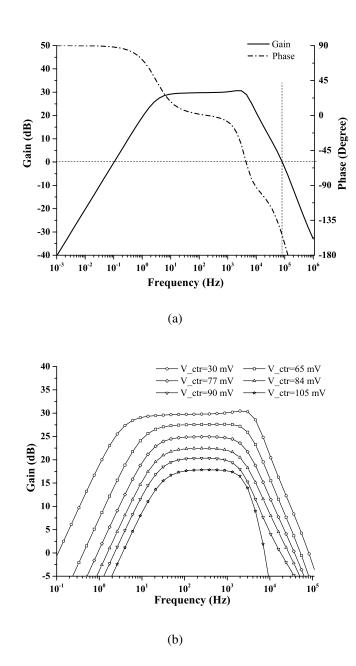

| 11 | (a) Frequency response of the proposed amplifier. (b) The variation of gain         |    |

|    | controlled by different V_ctr. $\ldots$                                             | 25 |

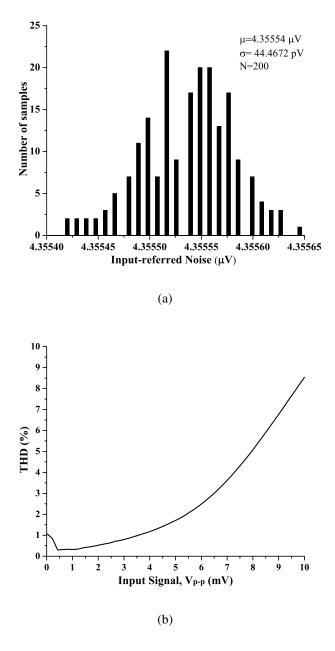

| 12 | (a) Monte Carlo simulation of input-referred noise. (b) The THD of output signals   |    |

|    | at different input peak-to-peak amplitudes                                          | 26 |

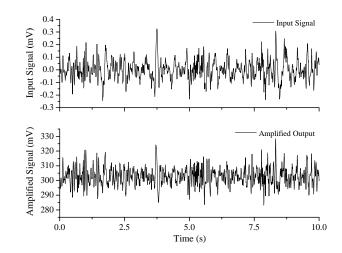

| 13 | Performance verification of the proposed amplifier with EEG signals                 | 27 |

| 14 | (a) The overall schematic of the proposed biopotential amplifier, (b) The schematic |    |

|    | of the operational transconductance amplifier (OTA).                                | 30 |

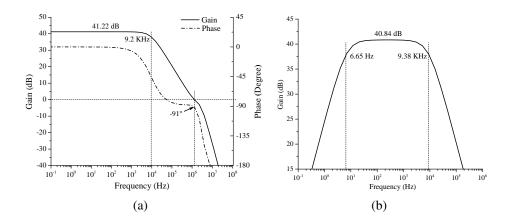

| 15  | (a) The frequency response of the proposed OTA, (b) The frequency response of                                      |    |

|-----|--------------------------------------------------------------------------------------------------------------------|----|

|     | the proposed biopotential amplifier                                                                                | 36 |

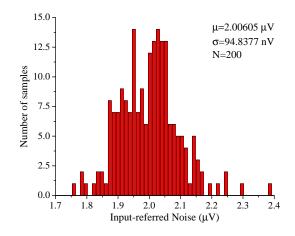

| 16  | Monte Carlo simulation results of the input-referred noise                                                         | 36 |

| 17  | Input EEG signal and amplified output                                                                              | 37 |

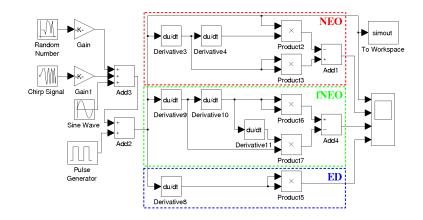

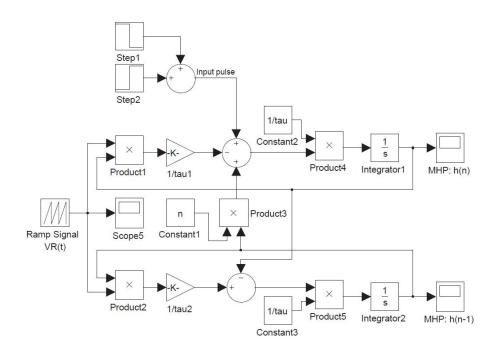

| 18  | Simulink models of NEO, fNEO and ED.                                                                               | 43 |

| 19  | Simulink algorithm simulation results of three methods. Input signal: a combination                                |    |

|     | of neural spike signals, Gaussian white noise, and baseline interferences                                          | 44 |

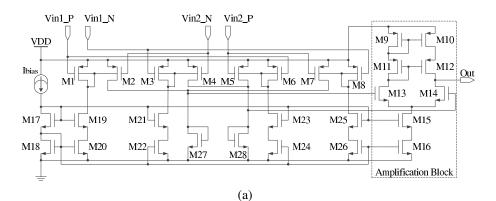

| 20  | The major building blocks of NEO spike detectors: (a) Multiplier, (b) Derivative, and (c) Adder.                   | 45 |

| 0.1 |                                                                                                                    | 15 |

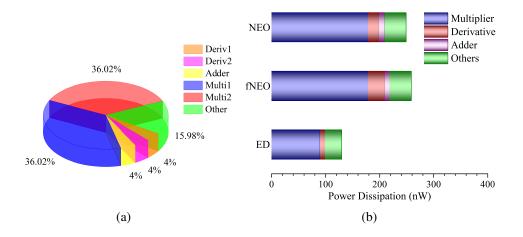

| 21  | (a) Power budget of a conventional NEO spike detector, (b) Power dissipation of NEO, fNEO, and ED spike detectors. | 47 |

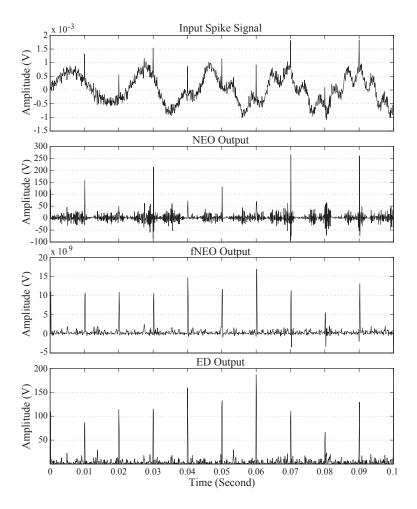

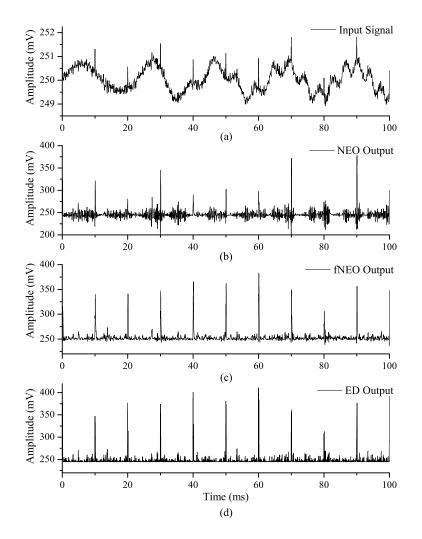

| 22  | Cadence circuit simulation results of three spike detectors. (a) Input signal: a                                   |    |

|     | combination of neural spike signals, Gaussian white noise, and baseline interferences                              | 5, |

|     | (b) NEO spike detector output, (c) fNEO spike detector output, (c) ED spike                                        |    |

|     | detector output.                                                                                                   | 48 |

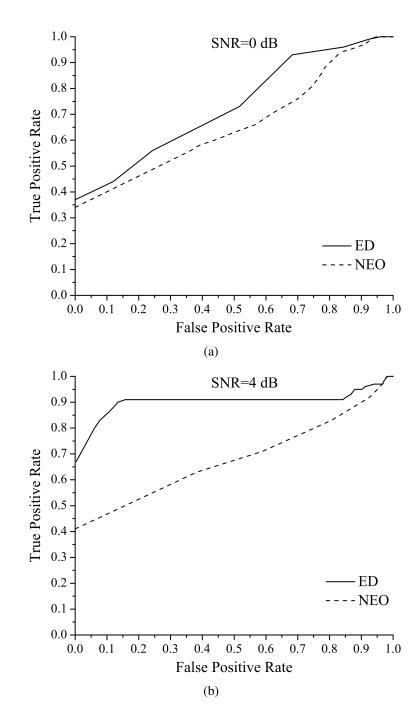

| 23  | (a) The receiver operating characteristic (ROC) curves of the proposed ED spike                                    |    |

|     | detector and NEO spike detector at SNR = $0 \text{ dB}$ , (b) The ROC curves of the                                |    |

|     | proposed ED spike detector and NEO spike detector at $SNR = 4 \text{ dB}.$                                         | 50 |

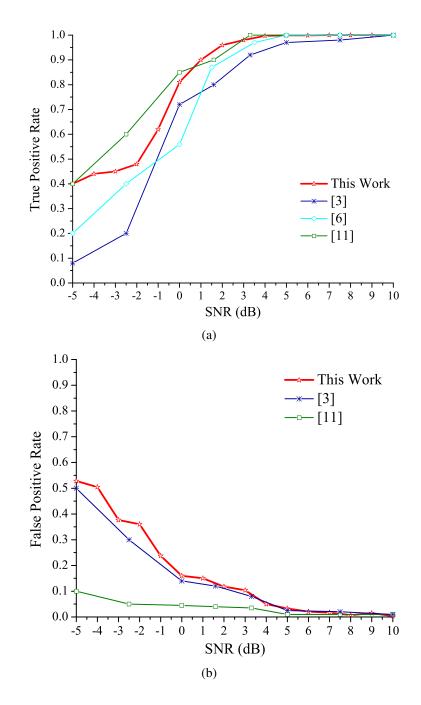

| 24  | (a) The comparison of TPR values at different SNR values, (b) The comparison of                                    |    |

|     | the FPR values at different SNR values.                                                                            | 52 |

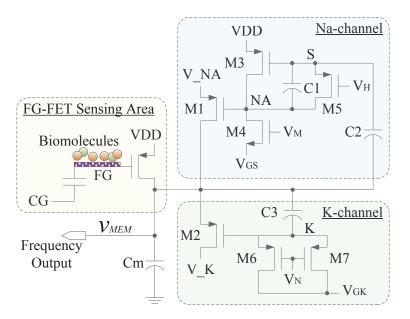

| 25  | Circuit schematic of the proposed neuromorphic CMOS sensor circuit. (CG:                                           |    |

|     | control gate; FG: floating-gate.).                                                                                 | 56 |

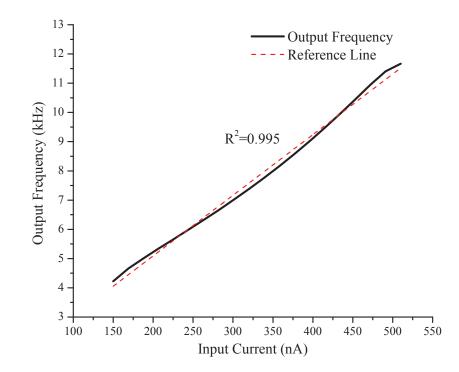

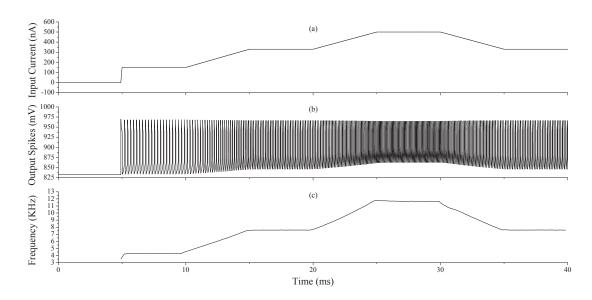

| 26  | The changes of the output frequency corresponding to the variation of input current.                               | 59 |

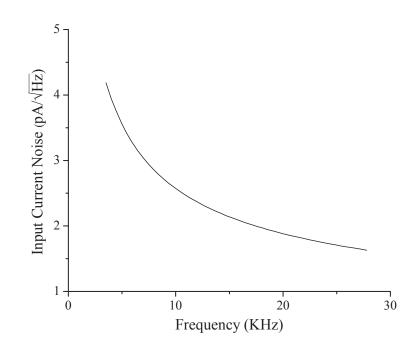

| 27  | Input current noise from 3.5 kHz to 27.8 kHz                                                                       | 61 |

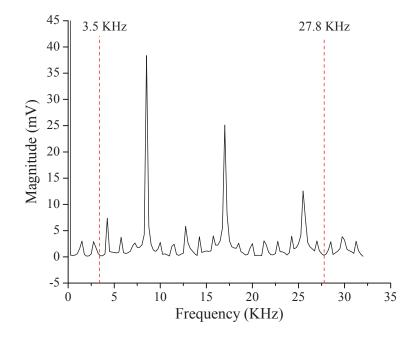

| 28  | The spectra of the output neural spikes for the 8.5 kHz frequency output                                           | 61 |

| 29 | The changes of the output frequency corresponding to the variation of the input            |    |

|----|--------------------------------------------------------------------------------------------|----|

|    | current amplitude                                                                          | 62 |

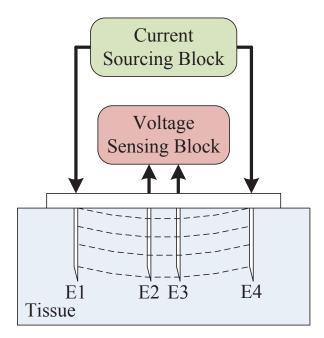

| 30 | The four-electrode configuration. E1 and E4 are current sourcing electrodes; E2            |    |

|    | and E3 are voltage sensing electrodes                                                      | 66 |

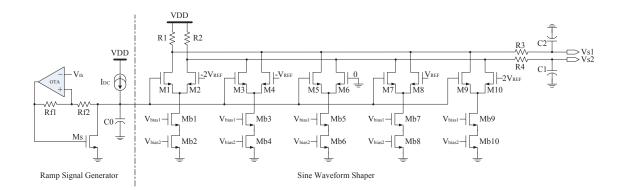

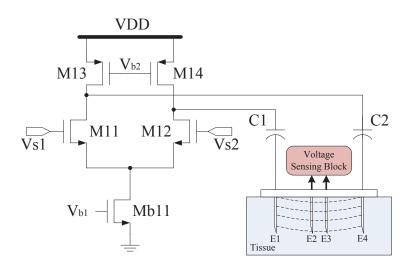

| 31 | The schematic of the proposed sinusoidal oscillator circuit                                | 66 |

| 32 | The schematic of the fully differential driver                                             | 69 |

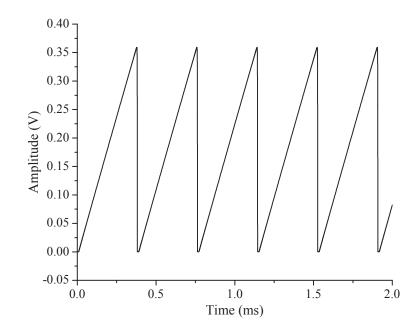

| 33 | The 2.6 kHz continuous ramp signal generated by the proposed ramp signal                   |    |

|    | generator                                                                                  | 71 |

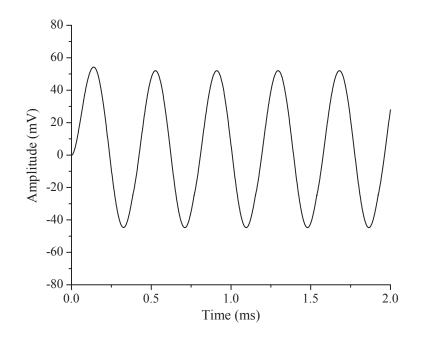

| 34 | The 2.6 kHz continuous sinusoidal signal generated by the proposed sinusoidal              |    |

|    | oscillator.                                                                                | 71 |

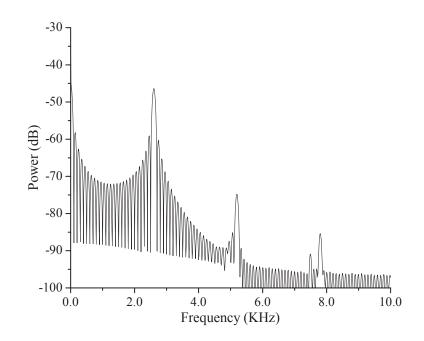

| 35 | The power spectral density of the 2.6 kHz sinusoidal signal shown in Fig. 34. $\therefore$ | 72 |

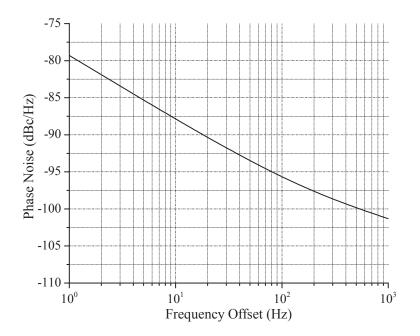

| 36 | The phase noise of the 2.6 kHz sinusoidal signal shown in Fig. 34                          | 72 |

| 37 | The Simulink block diagram of the proposed computation-efficient MHP set                   |    |

|    | generator                                                                                  | 76 |

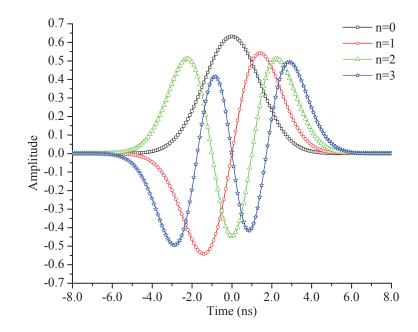

| 38 | The time responses of the normalized MHPs with n=0, 1, 2, 3. The pulses are                |    |

|    | normalized for the purpose of display.                                                     | 78 |

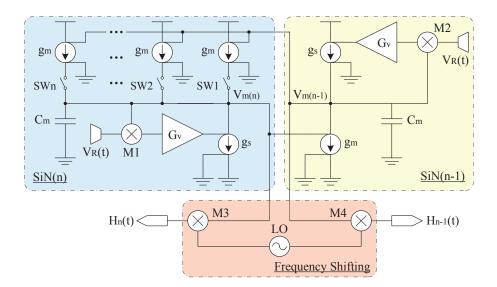

| 39 | The proposed neuromorphic MHP set generator. SW1-SWn represent the switches                |    |

|    | used to control the on/off of mutual interactive channels. LO represents a local           |    |

|    | oscillator with a frequency of 500 MHz. All the biasing circuits are omitted in the        |    |

|    | figure                                                                                     | 79 |

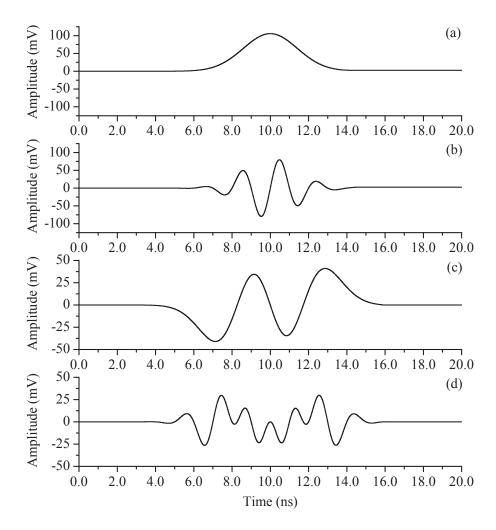

| 40 | The simulation results of the proposed MHP set generator. (a) The zero order               |    |

|    | derivative of the MHP, (b) The zero order derivative of the MHP after 500 MHz              |    |

|    | frequency shifting, (c) The third order derivative of the MHP, (d) The third order         |    |

|    | derivative of the MHP after 500 MHz frequency shifting                                     | 81 |

| 41 | The power spectral density of the generated the zero order and the third order             |    |

|    | derivatives of MHPs after 500 MHz frequency shifting.                                      | 82 |

#### 1. INTRODUCTION

#### Background

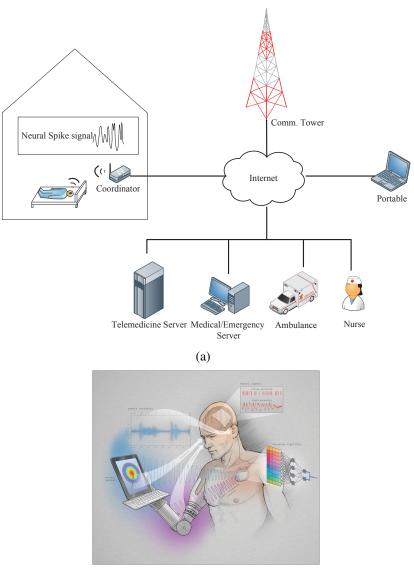

Along with the advances in microelectronics and wireless communications, a novel concept named 'ubiquitous healthcare' has been proposed nowadays. As shown in Fig. 1(a), a ubiquitous healthcare system offers doctors and nurses a more efficient way to monitor the health conditions of patients through communication network and Internet. Its telemetry attribute allows a continuous monitoring on the progression of chronic diseases, the body reaction to therapeutic drugs, and the post-operative recovery of patients. This continuous monitoring ensures a rapid response from healthcare providers when a disease outbreak occurs. In addition, the remote body inspection provided by the ubiquitous healthcare system benefits patients by saving their time and money. With the help of a ubiquitous healthcare system, the patients do not need to go to hospitals and spend about one entire day there. Instead, they only need to contact their doctors from their homes and get the inspection results rapidly, which saves the cost of transportation and the outpatient services.

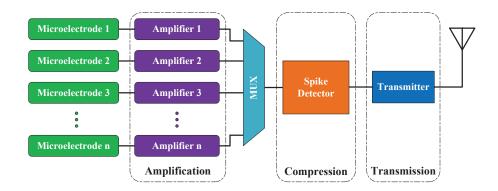

A low-power multichannel telemetry system which can achieve multichannel neural recordings wirelessly is the most critical component in the healthcare system. The detection sensitivity and the transmission speed of a telemetry system determine the integrity and the fidelity of the recorded neural signals which influence the performance of the healthcare system directly. In addition, a miniaturized telemetry system can be implanted into the brain and be used to develop a brain-machine interface (BMI) for paralyzed patients. As shown in Fig. 1(b), an implantable multichannel telemetry system can control a robotic arm to move objects for disabled people. A block diagram of a typical multichannel telemetry system is drawn in Fig. 2. The system can be divided into three stages: an amplification stage usually has multiple recording channels which provide the necessitated high spatial resolution for neural signals. Among them, each channel has a biopotential amplifier which

is used to amplify the target signal without introducing detectable circuit noise. The data compression stage is typically realized with a spike detector. The spike detector can identify the neural spikes from background signals and therefore removes the redundant data in the recording. By incorporating a spike detector, a telemetry system can effectively reduce the data volume and relaxes the bandwidth requirement on wireless data transmission. The last stage of a telemetry system is a wireless transmitter. This is the most important stage of a telemetry system and is also the bottleneck of high-speed neural recordings. The contradiction between power dissipation and data rate creates the principal challenge in the design of a telemetry system.

#### Motivation

Wireless multichannel neural recordings are very useful in today's neuroscience research, clinical diagnosis and for the development of healthcare devices. Owing to its wireless feature, a multichannel telemetry system eliminates the risks of skin rupture and body infection on subjects. By excluding the use of a large bundle of transcutaneous wires, wireless recordings offer neuroscience researchers the opportunity to investigate neuronal activities of freely behavioring animals. In addition, without the space limit caused by the physical sizes of wires, it is possible for a multichannel telemetry system to integrate more channels in a small area. As biological nerves typically have a high neuronal density, this multichannel high-density recordings provide valuable high spatial resolution information concerning the propagation of neuronal signals. For neuroscience research, this high-speed multichannel neural recordings allow neurologists to study the functionality of each neuron in a neural network. For clinical applications, high spatiotemporal resolution neuronal signals have multiple applications, such as disease prediction, medical diagnosis and drug evaluation. For advanced medical device developments, high-speed multichannel neural recordings help engineers improve the control and movement accuracy of neuroprosthetic devices. Despite having all these merits, high-speed multichannel neural recordings are

(b)

Figure 1: (a) A ubiquitous healthcare system. (b) An implantable multichannel telemetry system used for BMI robotic arm control. (Picture is from Nathan C. Rowland, etc. 2013 [1])

difficult to be obtained due to the challenges in the design of a low-power multichannel telemetry system.

The development of a low-power multichannel telemetry system for high-speed wireless neural recordings are challenging in multiple technical aspects. The most important one is the power dissipation of the system. Since a heat flux of 80 mW/cm<sup>2</sup> can cause the

Figure 2: The block diagram of a multichannel telemetry system. MUX: multiplexer.

necrosis of surrounding tissues [2][3], a low-power design which means low tissue heating is mandatory for the purpose of safety. As the increase of recording channels, the power budget assigned to each recording channel is further reduced. In addition, low power dissipation guarantee a chronic use of devices without frequent battery recharging or energy harvesting. A lower power dissipation allows the use of a smaller battery that makes smallsize and light-weight system possible. In account of these challenges, minimizing power dissipation of the system should be the priority in the design. The second challenge is the detection sensitivity of the system. Since neural signals [4] are typically in the range of 10  $\sim 500 \ \mu V$  with a noise level of  $5 \sim 10 \ \mu V_{rms}$ , a low-noise high-gain amplification stage [2] is required for high sensitivity detection. A study on low-power low-noise amplifiers is important for the development of the system. The third challenge is the transmission data rate. The increase on the number of channels causes a growth on data volume resulting in a significant problem for wireless data transmissions. For instance, if a system has 128 channels and each channel has 8-bit resolution at the Nyquist sampling rate requires 20 Mb/s data rate, the target signal is 10 kHz [5]. As the number of channels increases, the data rate will reach 100 Mb/s and even higher [6]. To achieve this data rate, a data compression stage and a high-speed wireless transmission stage are needed in the system. However, both of them must be designed under a constraint power budget. Last but not least, a system-onchip (SoC) architecture is preferred in most of the design, which prevents the use of large capacitors and inductors.

#### 2. LITERATURE REVIEW

In order to achieve all the functions with the minimum power dissipation, pioneering researchers have made great efforts on the design of biopotential amplifiers, spike detectors, and wireless transmitters.

A biopotential amplifier [2]-[7] which acts as the first amplification stage is one of the most important components in an implantable neural recording microsystem. The performance of a biopotential amplifier determines the complexity of the post signal processing. A well-designed low-power low-noise amplifier can improve the system sensitivity, dynamic range and power-efficiency. In the recent years, multiple high performance biopotential amplifiers [4]-[13] have been reported by pioneering researchers. Some of the research groups [4], [13] have designed the biopotential amplifier with input-referred noise values in the range of 2 ~ 4  $\mu V_{rms}$ , but the power dissipation is usually larger than 10  $\mu$ W. On the other side, some of the studies have developed amplifiers [9] with microwatt or sub-microwatt power dissipation, but the input-referred noise values are generally above 10  $\mu V_{rms}$ . However, as the advances of neurobiology, high-sensitivity high-precision recordings have become a mandatory. It requires the design of amplifiers with  $\sim 2 \mu V_{rms}$  inputreferred noise while dissipating only a few microwatt power. To strike a balance on the noise performance and power dissipation, a numeric value called noise efficiency factor (NEF) [2] has been widely used by the researchers to evaluate the power-noise efficiency of their designs. A smaller NEF value indicates a higher power-noise efficiency which is preferred for a design.

A carefully designed spike detector can effectively reduce the power dissipation of a microsystem by minimizing the transmission data. Given the low occurrence rate of neural action potentials (APs), about 10 to 120 occurrences per second, it is promising to achieve a great data compression by removing the redundant data at the intervals of spikes. Although

a spike detector itself may dissipate some extra power, but comparing with the power reduction brought by the data compression, up to 5 times as reported [14], introducing a low-power spike detector is till an energy-efficiency policy. A spike detection algorithm is the core of a spike detector. A variety of mathematical tools have been employed for the studies of the spike detection algorithms, such as thresholding [15], spike derivatives [16], and energy operators [17]. Because of its low computation complexity, robust and unsupervised features, the nonlinear energy operator (NEO) [17]-[20] has become the mostly used spike detection method. The low power implementations of NEO spike detectors have been extensively reported in the past years. Based on the sub-threshold design, a NEO spike detector [18] achieves a power dissipation of 2.7  $\mu W$ . Another study [19] combining the NEO spike detector and the spike feature extractor together dissipates only 1  $\mu W$  power. A NEO spike detector [20] which improves the detected waveform integrity has achieved a power dissipation as low as 780 nW. However, these studies only target on the noise degraded spike signals and fails to address the impact of large-amplitude baseline disturbance on the spike detections. This disturbance that is a mixture of local field potential (LFPs) and APs from neighbouring neurons may have an amplitude as high as 1 mV with frequency content up to 200 Hz [21]. Since LFPs contain valuable information for the clinic applications, such as epileptic seizure [22], it is highly desirable to investigate a robust method for the spike detection at the presence of the LFP.

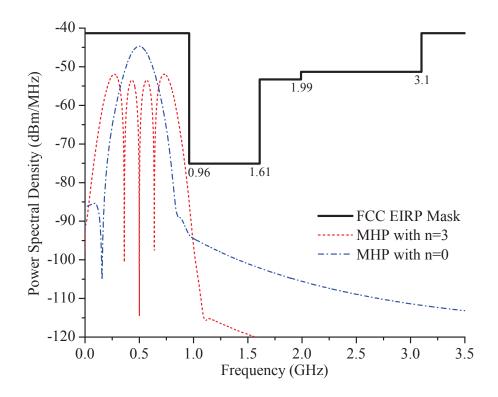

In wireless data acquisitions, the advances in micro-electromechanical systems (MEMS) have made it possible to integrate more recording channels in a small area. However, this increase on the number of channels causes a growth on data volume resulting in a challenge for wireless data transmissions. For example, a 128-channel recording system with 8-bit resolution at the Nyquist sampling rate requires 20 Mb/s data rate when the target signal is 10 kHz [**5**]. As the number of channels increases, the data rate reaches 100 Mb/s and higher [**6**]. Impulse radio based ultra-wideband (IR-UWB) communication can be a excellent strategy for high-speed neural recordings [**5**][**6**]. Sub-GHz UWB communications occupy a lower band (0 - 960 MHz) [**23**] than the standard UWB communications (3.1 -

10.6 GHz). The relatively lower frequency spectrum relaxes the system requirements on the circuit design and the communication synchronization, which ultimately reduces total power dissipation of the system. In addition, the sub-GHz UWB pulses have been proven to hold low attenuation in air, good penetration and little group delay [23][24].

#### 2.0.1. Research Approaches

In this study, we have employed the approach of application-specific integrated circuits (ASIC) design which customizes the circuit based on the requirements of the system. A carefully designed ASIC system uses the minimum power to achieve all functionalities. For amplification stage, we have utilized CMOS weak inversion design to achieve an ultra low-power low-noise signal amplification. For data compression stage, NEO based spike detection method has been studied to implement an ultra low-power spike detection. For data transmission stage, we have investigated the sub-GHz UWB transmitter. Through an in-depth study on the mathematical model of pulse generations, a low-power pulse generator has been investigated for sub-GHz UWB communications.

#### 2.1. Specific Aims

The objective of this dissertation is to develop a low-power multichannel telemetry system for high-speed wireless neural recordings. In order to achieve this goal, we have demonstrated three subsystems with a 0.13- $\mu$ m CMOS process: a low-power low-noise biopotential amplifier, an ultra-low-power high sensitivity spike detector and a power-efficient pulse generator. The three specific aims are described as follows:

# 2.1.1. Aim 1: Development of a low-power low-noise biopotential amplifier for signal amplification

For identical overall power dissipation, the increase of channel numbers shrinks the power budget assigned to each biopotential amplifier, because each channel requires one amplifier. On the other hand, as neural signals are typically in the range of  $10 \sim 500 \ \mu\text{V}$  with a noise level of  $5 \sim 10 \ \mu\text{V}_{rms}$  [2], a low-noise amplification is desired in practical applications. The aim of this work is to customize an amplifier which holds an optimized performance on power dissipation, device noise, and voltage gain for neural signal amplifications. To achieve this aim, we have employed the subthreshold CMOS circuit design to achieve a maximized power efficiency  $(g_m/I_D)$ . Two specific amplifiers have been studied. The first one is targeted to the application requiring very-large-scale neural recordings which generally demands the number of recording channels up to 1000. For this application, a biopotential amplifier needs to achieve an extremely low power dissipation (~100 nW). The second amplifier is target on low-noise performance which is critical for high-sensitivity neural recordings. A gain-tunable feature have been investigated in this amplifier to fully explore the resolution of analog-to-digital (ADC) block.

# 2.1.2. Aim 2: Development of a low-power high-sensitivity spike detector for data compression

Data compression stage is required due to the large data volume caused by the increase of recording channels. Neural spike detectors can effectively reduce the total power dissipation of the system by minimizing the transmission data. The aim of this work is to develop a spike detector to achieve a continuous high-sensitivity spike detection. To achieve this goal, two specific tasks must be completed. The first one is the investigation of spike detection algorithms. An efficient spike detection algorithm can enhance the detection sensitivity and lowers the power dissipation of a spike detector. The second task is to implement the proposed algorithm into a low-power high-sensitivity spike detector.

#### 2.1.3. Aim 3: Development of a power-efficient pulse generator for data transmission

A pulse generator is the most important component for a UWB transmitter. The aim of this work is to develop a power-efficient pulse generator for high-speed wireless neural recordings. The strategy is to develop an orthogonal pulse based sub-GHz UWB transmitter that can achieve a high data rate (up to 100 MHz) with pure pulse shape modulation. However, the design of an orthogonal pulse generator is complicated in both mathematical modelling and circuit implementation, which may result in a very high power dissipation and cannot be used for a neural recording system. In this study, we have made a balance on the power dissipation and data rate, and proposed a power-efficient orthogonal pulse set generator.

#### 3. BIOSIGNAL AMPLIFIERS

#### An Ultra-Low-Power Bioamplifier

Power dissipation of bioamplifiers has become one of the most critical factors for up-to-date implantable neural recording microsystems as the increasing of recording channels. This study presents an ultra-low-power bioamplifier [**25**] which is designed for the very-large-scale integration of neural recordings. To reduce the power, the proposed bioamplifier is designed to work with a 0.5 V power supply and all MOSFETs operate at weak inversion region. Both folded-cascode and wide-swing structures are employed to fully exploit the output swing. By producing a 18:1 bias current ratio between input transistors and load current mirror, the noise performance of the proposed bioamplifier is optimized for the given power dissipation. Designed in a 0.13- $\mu$ m CMOS process, the proposed bioamplifier consumes only 61.7 nW power to obtain a gain of 23.8 dB and a bandwidth of 3.6 kHz. The input-referred noise over the entire bandwidth is 12.7  $\mu$ V<sub>rms</sub>, corresponding to a noise-efficiency factor of 3.1.

#### Introduction of Ultra-Low-Power Bioamplifier

Access to simultaneously recorded bioelectrical activities from a large number of recording sites facilitates a more accurate diagnosis of the malfunctions in human body. Multielectrode biopotential recordings using an array of microelectrodes have become a standard practice in neuroscience research [2]. Implantable neural recording systems enable *in situ* recording of simultaneous neural activities [26]. A fully implantable neural recording system must be small enough for the convenience of implantation, while its power consumption must be low enough for the length of device lifetime and also for the safety of surrounding tissues.

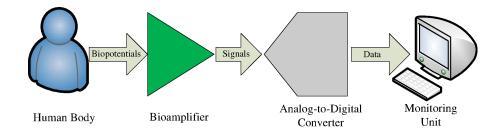

Figure 3: Biopotential recording system.

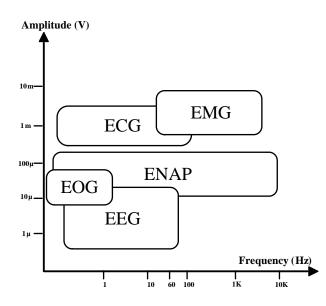

A bioamplifier is the most important component for a multielectrode biopotential recording system in terms of functionality. It is also a critical factor dictating the size and power dissipation of the system. A typical biological signal monitoring system is shown in Fig. 3. The bioamplifier needs to amplify biosignals in the range 10  $\mu$ V - 500  $\mu$ V with noise level of 5  $\mu V_{rms}$  - 10  $\mu V_{rms}$ . The characteristics of typical biosignals are shown in Fig. 4. Therefore, a high gain amplifier with a high signal-to-noise ratio (SNR) is desirable. Besides, since a heat flux of 80 mW/cm<sup>2</sup> can cause necrosis in muscle tissue [**2**], for an array of 512-electrodes, power dissipation must be less than 1  $\mu$ W per channel for a small chip area [**9**]. All these constraints must be considered while designing a bioamplifier.

The design of bioamplifiers has attracted the interest of multiple research groups in the past decades. Harrison *et al.* have reported a bioamplifier designed in 1.5- $\mu$ m CMOS process with a power dissipation of 80  $\mu$ W and a noise-efficiency factor (NEF) of 4 [**2**]. A sub-microwatt low-noise amplifier [**7**] is designed for neural recording consuming only 805 nW. Kim *et al.* have proposed a 220 nW neural amplifier [**9**] with an NEF of 2.47. Most of the reported studies consume  $\mu$ W level power with a few exceptions. However, the high power consumption hinders the accommodation of larger number of recording channels in an implantable system. For an energy-harvested system, the power budget become even more stringent to meet the noise efficiency while supporting higher number of channels. In an effort to reduce the power consumption of an implantable bioamplifier while maintaining desirable noise efficiency factor, our group is focusing on the design of an ultra-low-power bioamplifier which can eventually support large array neural signal recording.

Figure 4: Characteristics of typical biosignals.

In this work, we propose a power and noise efficient bioamplifier for large array biopotential recording systems. The proposed bioamplifier utilizes a differential folded-cascode gain stage and a common-gate gain stage to amplify the biological signal. The wide-swingcascode structure is employed to achieve high gain under low-voltage low-power operation. Subthreshold region operation of MOSFETs are utilized and the corresponding device dimensions are optimized by extensive computer simulations. The optimum trade-off of power, noise and device dimensions results in an ultra-low-power biosignal amplifier. The proposed bioamplifier is designed using 0.13- $\mu$ m standard CMOS process. Monte Carlo simulation is performed to validate the system performance with respect to device dimension mismatch. Finally, a pre-recorded human electroencephalography (EEG) signal is used to confirm the performance of the proposed bioamplifier.

#### Proposed Ultra-low-power Bioamplifier

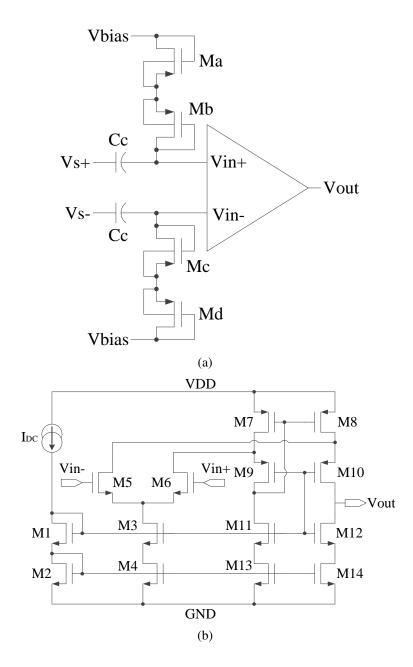

A high-pass filter shown in Fig. 5(a) is applied before the proposed bioamplifier to block the DC-offset which is produced by the skin-electrode interface. The core circuit of the proposed bioamplifier is shown in Fig. 5(b). The folded-cascode structures consisting of MOSFETs operating in weak-inversion-saturation and deep-weak-inversion regions is utilized in the proposed architecture to achieve high gain with low-power consumption.

The NMOS differential pair  $(M_5, M_6)$  working in the weak-inversion-saturation acts as the first gain stage of the proposed bioamplifier. The gate terminals of  $M_5$  and  $M_6$ , Vin + and Vin-, are the differential inputs. NFETs are selected here instead of PFETs to ensure a high transconductance which is important for the noise suppression. The primary challenge of designing a bioamplifier is the use of constraint power budget to achieve a low-noise performance and decent signal gain. A bias current ratio of 18:1 is achieved on the drain current of transistor  $M_5$  and the drain current of transistor  $M_{10}$ . The large bias current on the input NMOS pair produces large transconductances of  $M_5$  and  $M_6$  which yield a high gain on the first stage and reduce the input-referred noise of the bioamplifier.

The gain function of the input NMOS differential block can be given by

$$G_{1} = -g_{m5} \cdot \left[ r_{o8} || \frac{1}{g_{m10}} \left( 1 + \frac{g_{m12}r_{o12}r_{o14}}{r_{o10}} \right) || r_{o5} \right]$$

(3.1)

where  $G_1$ ,  $g_m$  and  $r_o$  represent the gain of the NMOS input differential block, the transconductance and the output resistance of the MOSFET, respectively. The output signals then pass through the common-gate gain stages ( $M_9$ ,  $M_{10}$ ) and the gain of these stages can be represented as

$$G_2 = g_{m10} \cdot (r_{o10} || g_{m12} r_{o12} r_{o14}) \tag{3.2}$$

where  $g_{m10}$  represents the transconductance of  $M_{10}$ . Finally, the total gain of the entire bioamplifier is

$$G = G_1 G_2 \tag{3.3}$$

where  $G_1$  and  $G_2$  are given by (3.1) and (3.2), respectively.

#### Noise analysis on the proposed bioamplifier

As the design is aimed to amplify neural signals, the proposed amplifier must holds a noise performance that is good enough to process micro-volts level signals. The amplitude of

Figure 5: (a) Bioamplifier with a high-pass filter for DC suppression. (b) Schematic of the proposed bioamplifier.

biological neural signal is in the range of  $50\mu V \sim 500\mu V$  and frequency ranges in  $10 \sim 3$  kHz [2] [10]. Thus flicker noise is the dominant noise and the input stage that contributes the most flicker noise is the most noisy part in the circuit.

To design a low-noise amplifier, we can lower the total noise by reducing the noise contribution of the first stage, i.e. the noise contributed by  $M_5 \sim M_8$ . The thermal noise of the first stage can be expressed as

$$e_{ni,al}^{2} = \frac{8kT\gamma}{g_{m5}} + \frac{8kT\gamma g_{m7,8}}{g_{m5}^{2}}$$

(3.4)

where k is the Boltzman constant and T is the absolute temperature.  $\gamma$  represents the drain noise coefficient. The flicker noise can be expressed as

$$e_{ni,flicker}^2 = \frac{2K_N}{C_{ox}(WL)_5 f}$$

(3.5)

where  $K_N$  represents the flicker noise coefficients, and  $C_{ox}$  is the gate oxide capacitance per unit area. Finally, the total input-referred noise can be represented as

$$v_{ni,rms} = \sqrt{\int_{BW} \left( e_{ni,thermal}^2 + e_{ni,flicker}^2 \right) df}$$

(3.6)

By inserting (3.4) and (3.5) into (3.11), the equation (3.11) indicates that the total inputreferred noise of the circuit can be reduced by enhancing the transconductances of  $M_5$  and  $M_6$ . Large dimensions  $\frac{348 \ \mu m}{360 \ nm}$  are used here to achieve high transconductance. Although the equation (3.4) also shows that by reducing the transconductance of  $M_{7,8}$  pair can also reduce the noise, it can not be easily achieved because  $M_{7,8}$  pair need to sustain a high current in the circuit which is the summation of current from input pair and output load. We applied a small aspect ratio,  $\frac{14 \ \mu m}{22 \ \mu m}$ , on  $M_{7,8}$  pair for the purpose of a high gain in the first stage.

To evaluate the noise performance of a low-power bioamplifier, a commonly used performance metric is the NEF [2] that is expressed as

$$NEF = v_{ni,rms} \sqrt{\frac{2 \cdot I_{total}}{4\pi kT \cdot U_T \cdot BW}}$$

(3.7)

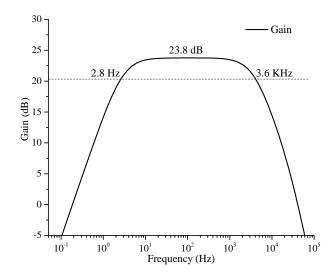

Figure 6: Gain and bandwidth profile.

where  $v_{ni,rms}$  is the root mean square of input-referred noise,  $I_{total}$  is the total current, k is the Boltzman constant, T is the absolute temperature,  $U_T$  is the thermal voltage (26 mV@300K) and *BW* is the bandwidth.

#### Simulation Results

This design uses a standard 0.13- $\mu$ m CMOS process and a 0.5 V supply. The proposed bioamplifier is designed and simulated with Cadence Virtuoso Spectre circuit simulator. The total power consumption including the high-pass filter is only 61.7 nW. In order to reduce flicker noise at the input stage, large dimensions  $\frac{348 \ \mu m}{360 \ nm}$  are used on the input differential pair  $M_5$  and  $M_6$ . The PMOS pair  $M_7$  and  $M_8$  sustain the largest drain current that prompts in a large drain noise. Therefore, to reduce the noise contribution, two PFETs have been used with a relatively small aspect ratio,  $\frac{14 \ \mu m}{22 \ \mu m}$ . Transistors  $M_9 \sim M_{14}$  form the load current mirror which are biased by small drain current to achieve low transconductance.

By driving a load capacitor of 2 pF, the proposed bioamplifier produces a frequency response as shown in Fig. 6 As is seen from the plot, the bioamplifier achieves a gain of 23.8 dB and a -3 dB bandwidth of 3.6 kHz. The lower cutoff frequency, 2.8 Hz, is decided by the value of  $C_P$  and MOS-bipolar transistors, while the higher cutoff frequency, 3.6 kHz,

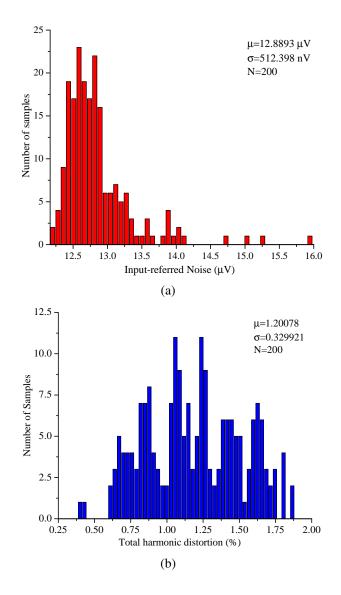

Figure 7: Monte Carlo Simulation. (a) Monte Carlo Simulation results of input-referred noise. (b) Monte Carlo Simulation results of THD when input  $V_{pp}$ =500  $\mu$ V.

is determined by the output load capacitor and output resistance. In this design,  $C_P$  is 100 pf and are implemented with two Dual-MIMCAP capacitors.

The proposed bioamplifier achieves a 12.7  $\mu V_{rms}$  input-referred noise in the noise simulation, that leads to a NEF of 3.1 under 61.7 nW power dissipation. Considering the process variation and mismatch of fabrication, Monte Carlo simulation is conducted to make a more practical assessment. Fig. 7(a) is the Monte Carlo simulation of input-referred noise with 200 samples. It produces a mean input-referred noise of 12.9  $\mu V_{rms}$  with only 0.5  $\mu V_{rms}$

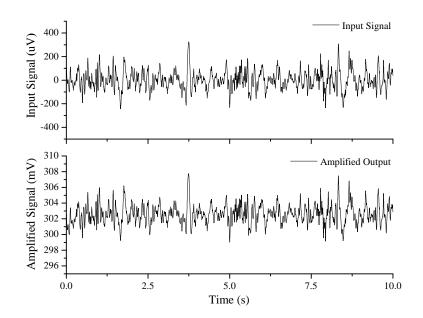

Figure 8: Input EEG signal and amplified output.

Figure 9: The layout of the proposed bioamplifier.

standard deviation. The relatively smaller standard deviation value indicates a robust noise performance of the proposed bioamplifier.

Linearity is another important parameter for an amplifier because it directly affects the dynamic range of amplifier and the fidelity of output signal. The transient simulation of

the proposed bioamplifier shows a 1% total harmonic distortion (THD) at the presence of 500  $\mu V_{pp}$  input signal. Given a typical neural action potential has the amplitude in the range of 50 ~ 500 $\mu V$  [27], the linearity of the proposed bioamplifer is qualified for neural signal recordings. To verify the design for fabrication, another Monte Carlo simulation is done and the results are shown in Fig. 7(b). For a 500  $\mu V_{pp}$  input signal, Monte Carlo simulation indicates a mean value of 1.2% THD and a standard deviation of ~ 0.33. The error between the transient simulation and the Monte Carlo simulation is due to the ultralow-power design and the open-loop topology of the proposed bioamplifier.

A human EEG signal from MIT-BIH Database is applied to the proposed bioamplifier and the simulation results are shown in Fig. 8. The output indicates an identical dynamics but with a 23.8 dB amplification. The design has been submitted for fabrication and the layout is shown in Fig. 9. A comparison of the proposed bioamplifier with several existing works is shown in Table 1. The proposed circuit has a comparable noise and linearity performance with the previously published works, but consumes much less power, only 61.7 nW.

|                           | [9]       | [12] | [13] | This work |

|---------------------------|-----------|------|------|-----------|

| Supply (V)                | $\pm 0.9$ | 1.5  | 1    | 0.5       |

| Gain (dB)                 | 28.9      | 37   | 40   | 23.8      |

| $f_L$ (Hz)                | 0.1-100   | 5    | 0.05 | 2.8       |

| $f_H$ (kHz)               | 11.2      | 7    | 10.5 | 3.6       |

| $v_{ni,rms}(\mu V_{rms})$ | 14.5      | 5.5  | 2.2  | 12.7      |

| NEF                       | 1.95      | 2.58 | 2.9  | 3.1       |

| $1\%$ THD ( $mV_{p-p}$ )  | -         | 0.40 | 1    | 0.5       |

| Power ( $\mu$ W)          | 0.22      | 1.5  | 12   | 0.061     |

| Technology (µm)           | 0.35      | 0.13 | 0.13 | 0.13      |

| Year                      | 2009      | 2011 | 2012 | 2012      |

Table 1: Comparison of the Proposed Bioamplifier with the Previously Reported Works

#### Summary of Ultra-Low-Power Bioamplifier

In this study, we present the design of an ultra-low-power bioamplifier for biological signal recordings. Folded-cascode structure and subthreshold MOSFETs are used for low-power

low-noise amplification. The proposed amplifier has been designed and simulated in a standard 0.13- $\mu$ m CMOS process. This amplifier has a gain of 23.8 dB with 3.6 kHz bandwidth and consumes only 61.7 nW from a 0.5 V power supply. The proposed amplifier has an input-referred noise of 12.7  $\mu V_{rms}$  and a low NEF of 3.1.

#### A Low-Noise Gain-Tunable Amplifier

This study [28] presents a low-noise gain-tunable biopotential amplifier that is designed based on a folded-cascode structure. Sub-threshold and self-biasing techniques are employed to achieve a low-noise and low-power amplification. With a bias-current tuning block, the gain of the proposed biopotential amplifier can be precisely adjusted. Designed in a standard 0.13  $\mu$ m CMOS process, the proposed amplifier provides a 5.9 kHz bandwidth and 30.1 dB gain with 732 nW power. The input-referred noise over the entire bandwidth is 4.3  $\mu$ V<sub>rms</sub>, equivalent to a noise-efficiency factor of 2.48.

#### Introduction of Low-Noise Gain-Tunable Amplifier

A biopotential amplifier [2][7] that amplifies neural signals at the front-end is one of the most important components of an implantable neural recording microsystem. Since neural signals typically range from 10  $\mu$ V to 500  $\mu$ V with a noise floor of 5 - 10  $\mu$ V<sub>rms</sub>, biopotential amplifiers must achieve both high gain and low-noise performance. Low-noise amplification is extremely important since it determines the sensitivity of the entire system as well as impacts the capacity of post-processing. Furthermore, due to the diversity of neural signals, different bandwidth ranges are expected to record different biosignals [29]. Finally, for all implantable circuit designs, power dissipation must be considered carefully since excessive power consumption will not only shorten the longevity of batteries but also cause the necrosis of tissues [30].

State-of-the-art biosignal amplifiers have achieved microvolt input-referred noise and sub-microwatt power dissipation. A neural amplifier [9] is reported to consume only 220

nW power with 14.5  $\mu V_{rms}$  input-referred noise. The work presented in [11], reduces the input-referred noise to 3.5  $\mu V_{rms}$  while consumes 7.92  $\mu W$  power. Recently, a biopotential amplifier [13] which has a power dissipation of 12  $\mu W$  achieves an input-referred noise of 2.2  $\mu V_{rms}$ . With an improved power consumption of 800 nW, a neural recording amplifier [31] maintains the input-referred noise at 5.71  $\mu V_{rms}$ .

In this work, we present a gain-tunable biopotential amplifier that achieves an inputreferred noise of 4.3  $\mu V_{rms}$  with 732 nW power consumption. The self-biasing arrangement consisted of weak inversion MOSFETs is demonstrated to achieve the low-noise and low-power amplification. The precisely tunable gain of the proposed amplifier can maximally utilize the resolution of an analog-to-digital converter (ADC) by adjusting the amplitude of the amplified signal to the suited range.

Figure 10: Schematic of the proposed biopotential amplifier.

#### Design of Proposed Biopotential Amplifier

#### Gain analysis.

Gain of stages: As shown in Fig. 10, the proposed amplifier consists of two stages - a folded-cascode stage  $(M_1-M_{11})$  and an output stage  $(M_{12}-M_{15})$ . Transistors  $M_{16}$  and  $M_{17}$  are used to control the gain. Transistors  $M_{15}$ ,  $M_3$ , and  $M_{10}$  creates the self-bias structure

for the DC bias of folded-cascode stage. If we represent the bias current of output stage as  $I_{out}$ , the drain current of  $M_3$  and  $M_6$  can be denoted as  $\alpha I_{out}$  and  $\beta I_{out}$ , respectively where  $\alpha$  and  $\beta$  are constants. Then, the drain current of  $M_4$ ,  $I_{tot}$ , can be represented as:

$$I_{tot} = \frac{\alpha I_{out}}{2} + \beta I_{out} \tag{3.8}$$

By using EKV model [32] and ignoring the gain control block ( $M_{16}$  and  $M_{17}$ ), we can obtain the gain of the folded-cascode stage:

$$A_{1} = \frac{\left(nU_{T} + \frac{1}{\lambda_{8}\lambda_{10}nU_{T}}\right)\left(\frac{1}{\lambda_{8}\lambda_{10}(nU_{T})^{2} + 1}\right)}{2\left(\frac{\beta}{\alpha}\right)\left[\lambda_{4}(nU_{T})^{2} + nU_{T} + \frac{1}{\lambda_{8}\lambda_{10}}\right] + (\lambda_{1} + \lambda_{4})\left[(nU_{T})^{2} + \frac{1}{\lambda_{8}\lambda_{10}}\right]}$$

(3.9)

where  $\lambda$  and  $U_T$  represent the channel length modulation parameter and thermal voltage, respectively. The numeric in the subscript denotes the number of MOSFETs in Fig. 10. Similarly, the gain of output stage can be represented as:

$$A_2 = \frac{1}{\lambda_{15}(nU_T + \frac{1}{\lambda_{12}})}$$

(3.10)

The total gain,  $A_{OTA}$ , of the proposed amplifier is the multiplication of equations (3.9) and (3.10).

Gain control and bandwidth expansion: From equation (3.9), we may notice that  $\alpha$  is proportional to  $A_{OTA}$ , while  $\beta$  is inversely proportional to  $A_{OTA}$ . In other words, the selfbiasing arrangement of  $M_3$  and  $M_{16}$  in Fig. 10 constitutes a positive feedback, while  $M_{10}$ and  $M_{16}$  create a negative feedback. Consequently, we can adjust the gain of the proposed amplifier by changing the value of  $\beta$ . A gain control block is added in the dashed line area of Fig. 10. When V\_ctr rises, the drain current of  $M_{18}$  is increased. The current flow through  $M_{6,7}$  and  $M_{8,9}$  increases accordingly, which results in a bigger  $\beta$  value. As a result, the gain of the amplifier is decreased. In contrast, by lowering V\_ctr, we can increase the gain accordingly. However, the change of V\_ctr must keep all MOSFETs saturated in the weak inversion region. Both Miller feedback and external negative feedback are used on the proposed amplifier. Depicted in Fig. 10,  $C_m$  and  $R_m$  construct a miller feedback which improves the stability by raising the phase margin. External negative feedback,  $C_f$  and  $R_f$ , expands the -3 dB bandwidth effectively, but at the expense of a few gain drop.  $C_1$  and  $C_2$  are added to improve the phase margin.

*Noise Analysis.* Since the input stage dominates the total noise contribution, we can estimate the noise performance of the entire amplifier by analyzing the input-referred noise of the input stage. To simplify the math, we represent the thermal noise and flicker noise from the pairs of  $M_{1,2}$ ,  $M_{4,5}$ ,  $M_{6,7}$  as:

$$\overline{V_{n,in}^2} = 8kT\gamma \left(\frac{1}{g_{m1,2}} + \frac{g_{m4,5}}{g_{m1,2}^2} + \frac{g_{m6,7}}{g_{m1,2}^2}\right) + \frac{2K_N}{C_{ox}(WL)_{1,2}f} + \frac{2K_P}{C_{ox}(WL)_{4,5}f} \left(\frac{g_{m4,5}^2}{g_{m1,2}^2}\right) + \frac{2K_P}{C_{ox}(WL)_{6,7}f} \left(\frac{g_{m6,7}^2}{g_{m1,2}^2}\right)$$

(3.11)

where  $K_N$  and  $K_P$  are process-dependent constants;  $\gamma$  is MOSFET noise coefficient. The equation indicates that we can reduce both thermal noise and flicker noise by increasing the dimension of  $M_{1,2}$ . Although smaller  $g_{m4,5}$  and  $g_{m6,7}$  can also decrease the noise, lower transconductance will reduce the bandwidth of the amplifier. To strike a balance between noise and bandwidth, appropriate values of  $g_{m4,5}$  and  $g_{m6,7}$  are selected through simulation. Noise-efficiency factor (NEF) [2], which assesses noise performance along with power consumption and bandwidth, is also employed to make a complete evaluation on the proposed amplifier.

#### Simulation Results

The proposed biopotential amplifier is designed in a standard 0.13  $\mu$ m CMOS process. As shown in Fig. 11(a), the frequency response of the proposed amplifier indicates a 30.1 dB gain and 5.9 kHz bandwidth, and 30° phase margin. Fig. 11(b) shows the variation of the gain corresponding to the change of V\_ctr. By adjusting V\_ctr from 30 mV to 105 mV, the gain of the amplifier can be tuned from 30.1 dB to 17.5 dB ( $\sim$  -0.26 dB/mV). Fig. 12(a). presents the squared input noise over the -3 dB bandwidth of 3.4 Hz - 5.9

|                                | [ <b>9</b> ] <sup><i>a</i></sup> | [ <b>34</b> ] <sup>b</sup> | <b>[12</b> ] <sup><i>a</i></sup> | [ <b>11</b> ] <sup><i>a</i></sup> | [ <b>13</b> ] <sup><i>a</i></sup> | [ <b>31</b> ] <sup><i>a</i></sup> | This work <sup><math>b</math></sup> |

|--------------------------------|----------------------------------|----------------------------|----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-------------------------------------|

| $V_{ni,rms}$ ( $\mu V_{rms}$ ) | 14.5                             | 14.3                       | 5.5                              | 3.5                               | 2.2                               | 5.71                              | 4.3                                 |

| NEF                            | 1.95                             | 1.32                       | 2.58                             | 3.35                              | 2.9                               | 2.59                              | 2.48                                |

| $f_L$ (Hz)                     | 0.1                              | 0.024                      | 5                                | 10                                | 0.05                              | 0.2                               | 3.4                                 |

| $f_H$ (kHz)                    | 11.2                             | 7.47                       | 7                                | 7.2                               | 10.5                              | 5.8                               | 5.9                                 |

| Gain (dB)                      | 28.9                             | 28.3                       | 37                               | 39.4                              | 40                                | 40                                | 30.1                                |

| Supply (V)                     | $\pm 0.9$                        | 1.8                        | 1.5                              | 1.8                               | 1                                 | 1                                 | 0.55                                |

| Power ( $\mu$ W)               | 0.22                             | 0.077                      | 1.5                              | 7.9                               | 12                                | 0.8                               | 0.732                               |

| 1% THD ( $mV_{p-p}$ )          | -                                | -                          | 0.4                              | 5.7                               | 1                                 | -                                 | 3.6                                 |

| Process $(\mu m)$              | 0.35                             | 0.18                       | 0.13                             | 0.18                              | 0.13                              | 0.18                              | 0.13                                |

Table 2: Performance of the proposed amplifier and other state-of-art designs

*a*: represents measurement results; *b*: represents simulation results.

kHz, which is equivalent to an input-referred noise of 4.3  $\mu$ V<sub>rms</sub>. A NEF of 2.48 can be calculated accordingly with a power consumption of 732 nW. The linearity of the proposed amplifier is examined with total harmonic distortion (THD). Fig. 12(b) shows the THD of amplified signals corresponding to different input peak-to-peak amplitudes. For a 1% THD, the peak-to-peak input signal is 3.6 mV. In order to verify the performance of the proposed amplifier in amplifying the real biopotential signals, a 47 years old female human electroencephalography (EEG) signal [**33**] is applied to the amplifier. As is seen in Fig. 13, the spike of input EEG signal has a magnitude of 129.8  $\mu$ V, while the corresponding output spike achieves a magnitude of 4.4 mV. These values indicates an amplification of 33.9× or 30.6 dB, which is close to our ac simulation result of 30.1 dB gain. Table 2 summarizes the performance of this work and other state-of-art designs.

#### Summary of Low-Noise Gain-Tunable Amplifier

In this study, we have proposed an improved biopotential amplifier which achieves an inputreferred noise of 4.3  $\mu V_{rms}$ , corresponding to a NEF of 2.48. Owing to the subthreshold device and self-biasing scheme, the amplifier provides a 30.1 dB gain and 5.9 kHz bandwidth at the cost of only 732 nW power. The low-noise, low-power performance and tunable gain make the proposed amplifier promising in the applications of large array neural signal recordings.

Figure 11: (a) Frequency response of the proposed amplifier. (b) The variation of gain controlled by different V\_ctr.

Figure 12: (a) Monte Carlo simulation of input-referred noise. (b) The THD of output signals at different input peak-to-peak amplitudes.

# Amplifier With Optimized Noise Efficient Factor

Implantable wireless neural recording microsystems have demonstrated their efficacies in neuroscience studies in the past decades. However, with the advances of neurobiology, higher sensitivity and higher precision neural recording microsystems are becoming the

Figure 13: Performance verification of the proposed amplifier with EEG signals.

critical need. A biopotential amplifier is the first stage of a neural recording microsystem, the performance of which decides the signal-to-noise ratio and the power dissipation of each recording-channel. In this study, we present a low-noise biopotential amplifier with a noise efficiency factor (NEF) optimized closer to the theoretical limit of a folded cascode structure. A high transconductance input nMOSFET pair is designed to guarantee a low input-referred noise. A self-biased scheme comprising a weak positive feedback and a strong negative feedback is employed to further enhance the transconductance. By optimizing the noise performance while maintaining the NEF value close to the theoretical limit, a very low input-referred noise and a higher power-noise efficiency are achieved in our design. Using a standard 0.13- $\mu$ m CMOS process, the proposed amplifier achieves an input-referred noise of 1.98  $\mu$ V<sub>rms</sub> at the expense of 7.5  $\mu$ W power, corresponding to a NEF of 2.31. The gain of the proposed amplifier is 40.84 dB at a -3 dB bandwidth from 6.65 Hz to 9.38 kHz.

### Introduction of Amplifier With Optimized Noise Efficient Factor

High-density neural recordings have the potential to help neuroscientists and clinicians revealing neural network mechanisms. New emerging implantable wireless neural recording microsystems[**35**] which can monitor a large amount of neural activities wirelessly have made the research of freely behaving animals possible. However, the design of an implantable wireless neural recording microsystem is challenging due to the properties of neural signals and the power constraint of implantable devices. A neural signal[**4**] is typically in the range of  $10 \sim 500 \,\mu\text{V}$  with a noise level of  $5 \sim 10 \,\mu\text{V}_{rms}$ , which demands a high-gain and low-noise amplification. In addition, as a heat flux of 80 mW/cm<sup>2</sup> can cause the necrosis of tissues[**2**], a low-power design is not only extending the lifetime of battery but also ensuring the safety of tissues.

A biopotential amplifier [2]-[7] which acts as the first amplification stage is one of the most important components in an implantable neural recording microsystem. The performance of a biopotential amplifier determines the complexity of the post signal processing. A well-designed low-power low-noise amplifier can improve the system sensitivity, dynamic range and power-efficiency. In the recent years, multiple high performance biopotential amplifiers [4]-[13] have been reported by pioneering researchers. Some of the research groups [4]<sup>1</sup>[13] have designed the biopotential amplifier with input-referred noise values in the range of  $2 \sim 4 \,\mu V_{rms}$ , but the power dissipation is usually larger than 10  $\mu$ W. On the other side, some of the studies have developed amplifiers [9] (34) with microwatt or sub-microwatt power dissipation, but the input-referred noise values are generally above 10  $\mu V_{rms}$ . However, as the advances of neurobiology, high-sensitivity high-precision recordings have become a mandatory. It requires the design of amplifiers with  $\sim 2 \mu V_{rms}$  inputreferred noise while dissipating only a few microwatt power. To strike a balance on the noise performance and power dissipation, a numeric value called noise efficiency factor (NEF)[2] has been widely used by the researchers to evaluate the power-noise efficiency of their designs. A smaller NEF value indicates a higher power-noise efficiency which is preferred for a design.

In this work, we propose a low-noise biopotential amplifier with an NEF value close to the theoretical limit of the proposed circuit structure. The NEF theoretical limit of the proposed circuit topology is derived out first to guide the circuit design process. Based on this NEF value, we calculate the total current needed to achieve the highest power-noise efficiency. The very low input-referred noise is achieved by increasing the transconductance of the input nMOSFET pair. Three approaches are adopted here. Firstly, the nMOSFET pair are biased to operate at weak inversion saturation region for the high transconductance efficiency ( $g_m/I_D$ ). Secondly, 1/3 of the total current is assigned to the nMOSFET pair. Thirdly, a self-biased structure comprising a weak positive feedback and a strong negative feedback is applied on the circuit to further enhance the transconductance.

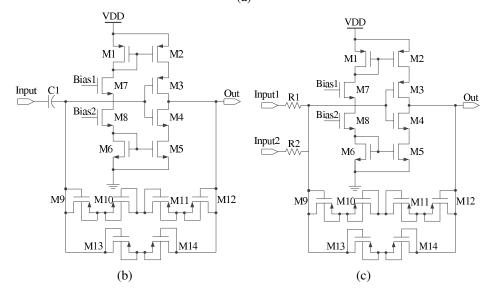

#### The Proposed Low-noise Biopotential Amplifier

The overall schematic of the proposed biopotential amplifier is shown in the Fig. 14(a). It consists of a high-pass filter stage and an operational transconductance amplifier (OTA) based gain stage. The high-pass filter is created by the capacitors  $C_a$ ,  $C_b$  and the equivalent resistors formed by the Miller effect of pseudoresistors  $M_a \sim M_d$ . The transistors  $M_a \sim M_d$  are MOS-Bipolar pseudoresistors[2] which have the resistance in the range of 10~100 G $\Omega$ . Due to their large resistance values, the negative AC feedbacks created by the pseudoresistors have very small currents, which allows the gain of the proposed biopotential amplifier close to the open-loop gain of the OTA. In addition, the pseudoresistor connections also provide the DC biases for the gates of the transistors  $M_1$  and  $M_2$ . By increasing the capacitances of  $C_a$  and  $C_b$ , a relatively small lower cut-off frequency can be obtained.

Fig. 14(b) shows the schematic of the proposed OTA circuit. The structure of the OTA circuit is based on the folded cascode structure. A 0.3 V bias voltage is applied on the gates of transistors  $M_7$  and  $M_8$ . Unlike conventional folded cascode amplifiers, self-biased connections are applied on transistors  $M_3 \sim M_6$  and  $M_9 \sim M_{10}$ . The reason to use the self-biased scheme is to form a positive feedback which can enhance the transconductance of the input nMOSFET pair. The positive feedback consists of transistors  $M_2$ ,  $M_5$ ,  $M_6$ ,

Figure 14: (a) The overall schematic of the proposed biopotential amplifier, (b) The schematic of the operational transconductance amplifier (OTA).

and  $M_{11}$ . The positive feedback mechanism can be explained as follows. When a neural signal is applied at the gate of transistor  $M_2$ , an amplified signal with 180° phase shift is generated at the drain of  $M_2$ . As transistor  $M_5$  does not provide any phase shift, the same signal appears at the gate of  $M_6$ . By introducing another 180° phase shift due to gate-drain signal transition created by the transistor  $M_6$ , the signal appears at the gate of  $M_{11}$  has the same phase as the input signal. As a result, when a high voltage signal presents at the gate of transistor  $M_2$ , a high voltage also appears at the gate of transistor  $M_{11}$ , which increases the drain current of transistor  $M_{11}$  and eventually increases the bias current of the input nMOSFET pair. Since the drain current is proportional to the transconductance when a MOSFET operates at weak inversion saturation region, the increased bias current raises the transconductance of the input nMOSFET pair. Subsequently, an even larger high voltage is generated at the gate of transistor  $M_{11}$  and further boosts up the transconductance of the input nMOSFET pair. This positive feedback can increase the transconductance of the input nMOSFET pair to a certain degree, but it also lowers the signal linearity and circuit stability. Therefore, considering the linearity and stability requirements, a weak positive feedback is employed in the design to leverage the high gain performance. To guarantee the stability and linearity of the proposed biopotential amplifier, a strong negative feedback comprising transistors  $M_8$  and  $M_{10}$  is created in the circuit. The operating principle of the

negative feedback can explained as follows. When the voltage at the gate of the transistor  $M_{11}$  rises, the drain current of the transistor  $M_{10}$  also increases resulting in a lower voltage at the drain of  $M_8$ . This reduces the voltage at the gate of transistor  $M_{10}$  and  $M_{11}$  and finally reaches a balanced output value.

We can obtain the gain of the proposed amplifier by deriving the gain of the OTA. Considering the perfect circuit symmetry, the transistor dimensions are identical for each pair, such as  $M_1 - M_2$ ,  $M_3 - M_4$ ,  $M_5 - M_6$ , etc. Thus, the gain of the proposed biopotential amplifier can be represented as